MOSFET

금속 산화막 반도체 전계효과 트랜지스터(영어: metal-oxide-semiconductor field-effect transistor)는 디지털 회로와 아날로그 회로에서 가장 일반적인 전계효과 트랜지스터 (FET)이다. 줄여서 MOSFET(한국어: 모스펫)이라고도 한다. 모스펫은 N형 반도체나 P형 반도체 재료 (반도체소자 참조)의 채널로 구성되어 있고, 이 재료에 따라서 크게 엔모스펫 (NMOSFET)나 피모스펫 (PMOSFET), 두 가지를 모두 가진 소자를 씨모스펫(cMOSFET, complementary MOSFET)으로 분류한다. (또한 일반적으로 nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, p-MOS FET. etc..라고도 함)

- MOS : metal-oxide-semiconductor

금속 산화막이란 이름이 붙은 것은 초기에 게이트로 금속을 이용하였기 때문이나, 현재는 폴리실리콘 게이트를 사용하여 금속이란 이름은 그저 관습적인 표현이 되었다. 저항층 게이트 전계효과 트랜지스터(insulated-gate field-effect transistor, IGFET)는 모스펫과 거의 동의어이며 산화되지 않은 게이트 저항층을 갖는 전계효과 트랜지스터를 가리킨다. 폴리실리콘 게이트를 갖는 소자를 가리킬 때 "IGFET"의 사용을 선호하지만, 아직도 대부분은 모스펫이라고 부른다.

일반적으로 사용된 반도체는 실리콘이지만 잘 알려진 IBM같은 어떤 칩 제조사는 모스펫 채널에 실리콘과 게르마늄 (SiGe)의 혼합을 사용하기 시작했다. 불행하게도 갈륨비소같이 실리콘보다 전기적 특성이 좋은 대다수의 반도체는 좋은 게이트 산화물을 형성하지 않고 이것은 모스펫에 적합하지 않다.

게이트 터미널은 채널에 위치한 폴리실리콘 (다결정 실리콘; 게이트에 폴리실리콘이 쓰이는 이유는 아래의 게이트 항목을 참조할 것)의 레이어이지만 전통적인 이산화 실리콘의 저항층 박막에 의하여 채널로부터 분리되었고 더 진보된 기술은 산소질화 실리콘을 사용하였다. 전압이 게이트와 소스 터미널 사이에 인가됐을 때 생성된 전계는 산화층을 관통하고 채널 아래에 소위 "역채널"을 생성한다. 역채널은 소스와 드레인처럼 P형이나 N형 동일한 형태여서 전류가 통과할 수 있는 전선관을 제공한다. 게이트와 바디사이의 전압을 다양하게 변화하는 것은 이 레이어의 전도를 조절하고 드레인과 소스 사이의 전류 흐름을 제어할 수 있게 한다.

회로 기호

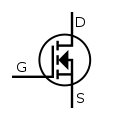

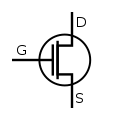

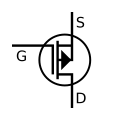

[편집]다양한 기호가 모스펫에 사용된다. 기초적인 모양은 일반적으로 직각으로 남겨져서 채널과 같은 방향으로 구부러진 소스와 드레인을 갖는 채널을 나타내는 선이다. 가끔 끊어진 선은 증가형과 공핍형을 위한 고체에 사용되지만 그림의 끊어진 선의 어색함은 이 구분이 종종 무시된다는 것을 의미한다. 다른 선은 게이트로 채널에 평행하게 그려진다.

보이는 대로 벌크 연결은 피모스나 엔모스를 나타내는 화살표를 갖는 채널의 뒤에 연결되어 보인다. 화살표는 항상 P에서 N으로 가리켜서 엔모스 (P우물이나 P기판에 N채널)는 안쪽을 가리키는 화살이 있다. 만약 벌크가 (일반적으로 부품소자의 경우처럼) 소스에 연결되어 있으면 트랜지스터를 떠나는 소스를 마주치기 위해 기울어진다. 만약 벌크가 (일반적으로 벌크가 공통인 IC 설계의 경우처럼) 보이지 않으면 역기호는 피모스를 가리키는 데 사용되기도 한다.

제이펫(JFET) 기호와 확장형과 공핍형 기호의 비교:

|

|

|

|

N채널 |

|

|

|

|

P채널 |

| 제이펫 | 모스펫 증가형 | 모스펫 공핍형 | ||

기호에서 벌크, 몸체, 터미널이 보인다. 여기서 내부적으로 소스에 연결되어 보인다. 이것은 일반적인 구성이며 아무의미없지만 중요한 구성이다. 일반적으로 모스펫은 4개의 단자 소자이고 집적회로에서 대부분의 모스펫은 몸체 연결을 공유하며 모든 트랜지스터의 소스단자에 연결할 필요가 없다.

모스펫 동작

[편집]금속 산화막 반도체 구조

[편집]

금속 산화막 반도체 (MOS)의 구조는 반도체 기판위에 이산화 규소 (SiO2)로 된 공핍층과 금속층 (실제로 금속대신에 폴리실리콘이 사용됨)을 쌓아서 얻어진다. 이산화 규소가 유전체(誘電體, dielectric) 물질이므로 평행판 축전기의 두 금속 전극 중에서 하나를 반도체로 대체한 것과 같은 구조이다.

전압이 모스 구조에 인가됐을 때, 반도체에 있는 전하의 분포를 변경한다. ( 양공 밀도를 갖는) P형 반도체를 고려하면 양의 (그림 참조)는 양공의 농도를 감소시키고 전자의 농도를 증가시키는 경향이 있다. 만약 가 충분히 크다면 게이트에 가까운 곳에서는 음전하 운반자의 농도는 양전하 운반자의 농도보다 높아지는데 반전층(inversion layer)이라고 한다.

P형 몸체를 갖는 이 구조는 N형 모스펫의 바탕이 되고 여기에 N형 소스와 드레인 부분을 추가하여야 한다.

모스펫 구조

[편집]

금속 산화막 반도체 전계효과 트랜지스터 (MOSFET)는 모스 축전기에 의한 전하농도의 변화에 기초를 두고 있다. 두개의 단자(소스와 드레인)는 각각 분리되어 고농도로 도핑된 영역에 연결되어 있다. 이런 영역은 P형이나 N형이 될 수 있지만 두개는 반드시 동일한 형태이어야 한다. 고농도 도핑 영역은 일반적으로 도핑 형태에 따라서 '+'로 (오른쪽에 있는 그림을 참조) 표시된다. 이 두 영역은 이와 반대 형(type)으로 도핑된, 몸체라고 알려진, 영역에 의하여 분리되어있다. 이 영역은 고농도 도핑이 아니며 '+' 기호가 없다. 활성 영역은 모스 축전기를 구성하며 세 번째 전극, 즉 게이트가 되어 몸체 위에 있으며 산화층에 의해 다른 모든영역과 절연되어 있다.

만약 모스펫이 N채널 즉 엔모스펫이면 소스와 드레인은 'N+' 영역이고 몸체는 'P' 영역이다. 양의 게이트-소스 전압이 걸리면(게이트에 양 전압, 소스에 음 전압) P반도체의 몸체와 N+도핑된 접합부의 공핍층이 좁아지고 산화층 아래에 있는 P 영역의 표면에 전자가 축적되어 반전층(inversion layer) 즉,"N채널"을 형성한다. 이 채널은 소스와 드레인사이에 걸쳐있지만 게이트 전압이 소스에서 채널로 전자를 끌어당기기에 충분히 클때만 그곳을 통하여 전류가 흐른다. 게이트와 소스사이에 영 또는 음의 전압이 걸리면 채널은 사라지고 소스와 드레인 사이에 전류가 흐르지 않는다.

만약 모스펫이 P채널 즉 피모스펫이면 소스와 드레인은 'P+' 영역이고 몸체는 'N' 영역이다. 음의 게이트-소스 (게이트에 음 전압, 소스에 양 전압) 전압이 걸리면 N반도체 내에 P+도핑된 접합부의 공핍층이 좁아져 산화층 아래에 있는 N 영역의 표면에 정공이 축적되 반전층이 생겨 P채널을 형성한다. 이 채널은 소스와 드레인사이에 걸쳐있지만 게이트 전압이 소스에서 채널로 양공을 끌어당기기에 충분히 작을때만 전류가 흐른다. 영 근처 또는 양의 전압이 게이트와 몸체사이에 걸리면 채널은 사라지고 소스와 드레인 사이 전류가 흐르지 않는다.

소스는 채널을 통하여 흐를 전하 운반자 (N채널에서는 전자, P채널에서는 양공)가 샘솟는(source) 곳이기 때문에 붙여진 명칭이다; 마찬가지로 드레인 (drain)은 전하 운반자가 채널을 빠져 나가는 곳이다.

동작 종류

[편집]

모스펫의 동작은 단자들에 걸리는 전압에 따라서 3개의 다른 영역으로 구분할 수 있다. 확장형 N채널 모스펫에서 동작 종류:

- 차단이나 역문턱 상태

- 일 때 여기서 는 소자의 문턱 전압(threshold voltage)이다.

- 기본적인 문턱모형에 따르면 트랜지스터는 차단되고 드레인과 소스사이의 전도는 없다. 사실은 전자 에너지의 볼츠만 분포로 인해, 소스에 있는 전자들중에서 에너지가 높은 일부분의 전자들이 채널로 들어가서 드래인으로 흐르는 것이 가능한데, 이것이 게이트-소스 전압의 지수 함수인 문턱아래 전류가 된다. 트랜지스터가 차단 스위치로 사용될 때 이상적으로는 드레인과 소스사이의 전류가 없어야 하지만, 미약한 역전류(inversion current)가 있어서 가끔 문턱아래 누설(subthreshold leakage)이라고 부른다.

- 선형 영역

- 와 인 경우.

- 트랜지스터가 켜지고, 채널이 형성되어 드레인과 소스사이에 전류가 흐르는 것을 허용한다. 모스펫은 소스와 드레인 전압과 관련된 게이트 전압에 의하여 제어되는 저항처럼 동작한다. 드레인에서 소스로의 전류는 아래와 같은 형태이다:

- 위의 는 전하 운반자의 유효이동도이며, 는 게이트 폭, 은 게이트 길이이고 는 단위면적당 게이트 산화층의 정전용량이다. 지수적인 역문턱 영역에서 선형 영역까지의 변화는 방정식의 제안처럼 예민하지 않다.

- 포화 영역

- 와 인 경우.

- 스위치가 켜지고, 채널이 형성되어 드레인과 소스사이에 전류가 흐르는 것을 허용한다. 드레인 전압이 게이트 전압보다 높아서 채널중의 일부분이 없어진다. 이 영역이 발생하는 것은 핀치오프라고도 알려져 있다. 드레인 전류는 이제 (일차 근사에서) 드레인 전압에 의존되지 않고 전류는 게이트-소스 전압에 의해서만 제어되며, 다음과 같은 형태이다:

- 채널 길이 변화 (얼리 효과)를 고려하기 위해 이 방정식에다 을 곱할 수 있다.

채널 길이가 아주 짧아지면, 전하 운반자의 이동은 유사-탄도성 전달(quasi ballistic transport)을 한다. 짧은 채널 효과가 크면, I-V 특성을 위의 방정식으로 근사시킬 수 없다. 차라리 포화 드레인 전류는 의 이차 함수가 아니라 거의 일차 함수에 가깝다.

몸체 효과

[편집]몸체 효과는 소스-벌크 전압의 변화에 의한 문턱 전압의 변화를 기술하며, 아래의 수식으로 근사된다:

,

위에서 는 영 기판 바이어스, 는 몸체 효과 변수, 는 표면 전압 변수이다.

몸체는 또다른 하나의 게이트처럼 동작할 수 있고 가끔 “뒷문(back gate)" 라고 불린다; 몸체 효과는 가끔 뒷문 효과라고도 불린다. (https://web.archive.org/web/20141110225738/http://equars.com/~marco/poli/phd/node20.html)

모스펫의 우수성

[편집]1960년에 벨 연구소의 강대원(姜大元, Dawon David Khang)과 마틴 아탈라(Martin Atalla)는 금속 산화막 반도체 전계효과 트랜지스터 (MOSFET)를 발명했다. 이론상으로 쇼클리의 트랜지스터와 달리 모스펫은 반도체 표면 위에 절연층을 얻은 다음 그 위에 금속 게이트 전극을 설치한다. 모스펫은 반도체로는 결정 실리콘을 사용하였고 절연층으로는 열로 산화된 이산화규소를 사용하였다. 뿐만 아니라 그것은 저렴한 생산비와 집적하기 쉬운 기술적 이점을 지녔으며, 실리콘 모스펫은 실리콘과 그것의 산화층 사이의 경계영역에 국부적인 전자 트랩 (경계 상태)을 생성하지 않고, 이전 트랜지스터의 성능을 떨어뜨리던 특성을 제거하였다. 이런 행운으로 떠오른 모스펫은 전자공학에서 주도적인 역할을 차지하게 되었다. 이것은 오늘날 정보 사회의 뿌리인 대규모 집적회로를 떠받치는 뜻밖의 발견이었다.

모스펫은 모든 실리콘 집적 회로의 기본요소가 되었다. 기본소자는 1920년대에 릴리언필드 (Lilienfeld)에 의하여 창안됐지만[1] 그는 소자를 만들기 위한 어떠한 기반도 없었다. 실리콘 평판 공정은 1950년대 후반에 맥칼딘 (McCaldin)과 호어니 (Hoerni)에 의하여 창안하고[2] 킬비 (Kilby)와 노이스 (Noyce)[3]에 의하여 창안된 집적회로는 릴리언필드의 소자가 현대시대에서 구현하는 것이 가능하게한 필요하는 기반이었다. 아탈라 (Atalla)와 강[4] 은 1950년대 후반에 현대의 모스펫을 설명하였고 홉스테인 (Hofstein)과 헤이만 (Heiman)은 1963년[5]에 실리콘 평판 공정 플랫폼에서 모스펫의 구조에 대하여 설명하였다. 그러나 이 평판 모스펫은 쇼클리, 바딘, 브래튼에 의하여 개발된 접합형 트랜지스터 (BJT)에 비교해서 큰 의미를 가지지 못했다.[6] 이 초기의 모스펫은 집적회로 설계에 사용하는게 매우 어려웠다. 왜냐하면 소스와 드레인을 고려한 게이트 배치의 불확실성과 게이트의 크기에 관련되어 느려지기 때문이다. 바우어 (Bower)[7]는 마스크나 템플릿으로 게이트와 연관된 소스와 드레인의 배치를 정의하는 게이트 구조를 이용하여 이런 문제들을 해결하였다. 이 간단한 단계는 게이트 배치의 불확실성을 제거하여 집적회로 설계문제를 해결하고 소자의 구성에서 사용되는 이론적으로 가장 작은 게이트를 제공하여 속도문제도 해결한다. 바우어와 딜 (Dill)[8] 은 금속이나 다결정(polycrystal) 실리콘으로 만든 스스로 정렬된 게이트 모스펫 (Self-Aligned-Gate MOSFET, SAGFET)을 설명하였다. 파긴 (Faggin)과 클라인 (Klein)은 1968년[9]에 패어차일드에서 활동 실리콘 게이트 공정을 개발하였다. 실리콘 게이트 SAGFET는 1970년대에 모든 현대의 집적회로에 의하여 선택하여 사용된 소자가 되어 BJT를 능가하였다. 삭펫 (SAGFET)은 인류 역사에서 인간이 만든 무기물 구조에서 가장 많이 생산하게 되었다.

디지털

[편집]마이크로프로세서같은 디지털 기술의 성장으로 모스펫 기술은 다른 실리콘기반 트랜지스터보다 빠르게 발전하게 되었다. 모스펫 성공의 주요 요인은 p-채널과 n-채널 모스펫을 기본소자로 사용한 디지털 시모스 논리회로의 개발이었다. 시모스 논리회로의 가장 큰 장점은 전류가 흐르지 않으므로(이상적으로) 논리 게이트에 대한 입력이 스위칭될 때를 제외하고는 전력 손실이 없다는 것이다. 시모스는 각 p모스펫을 n모스펫으로 보완하고 두개의 게이트와 두개의 드레인을 서로 연결하여 이것을 성취하였다. 게이트 전압이 높으면 n모스펫은 도전성을 띠고 p모스펫이 도전성을 띠지 않으며, 게이트 전압이 낮으면 이와 반대현상이 일어난다. 스위칭이 일어나는 시간 동안 전압은 상태가 바뀌며 짧은 순간 양쪽 모두 도전상태가 된다. 이와 같은 배치로 전력 손실과 발열이 현저히 감소한다. 집적회로에서는 더 많은 트랜지스터를 더 작은 칩으로 집적하기 때문에 과열은 중요한 해결과제였다.

디지털 스위치에서 모스펫의 또다른 이점은 게이트를 통하여 흐르는 DC전압을 방지하는 게이트와 채널사이의 산화층으로 더욱 전력소비를 감소시키고 입력 임피던스를 크게한다는 것이다. 게이트와 채널사이의 산화 절연층은 논리회로에서 한 단계의 모스펫을 선행단계 및 후행단계로부터 효과적으로 절연함으로써 하나의 모스펫 출력으로 다수의 모스펫 입력에 가할 수 있다. (TTL 같은) 접합형 트랜지스터를 기반으로 하는 논리회로는 이와 같은 높은 팬아웃 능력을 갖지 못한다. 이와 같은 절연에 의해 설계자는 독립적인 논리 단계사이의 부하 효과를 어느 범위까지 무시할 수 있다. 그 범위는 동작 주파수에 의하여 정해진다: 주파수가 증가할 때, 모스펫의 입력 임피던스는 감소한다.

아날로그

[편집]모스펫은 대부분의 디지털 회로에서 트랜지스터로 꾸준히 쓰이지만 아날로그 회로에서 여전히 우위를 차지하지 못한다. 접합형 트랜지스터는 높은 트랜스컨덕턴스와 독특한 특징들 때문에 전통적으로 아날로그 설계자의 선택을 받았다. 그럼에도 불구하고 모스펫은 아날로그 목적을 위해 널리 사용된다. 아날로그 회로의 특징과 성능은 모스펫의 크기(길이와 넓이)를 변화시켜 설계할 수 있다. 어떤 특정한 이중극 회로(bipolar circuit)에서만 이중극 소자의 크기가 영향을 미친다. 모스펫의 어떤 장점은 양의 온도계수때문에 발열로부터 접합형 트랜지스터가 한것처럼 고생하지 않아도 된다. 선형 영역은 정확한 저항처럼 사용하는 것이 가능하여 접합형 트랜지스터보다 훨씬 더 큰 제어 저항값을 가지고 있다. 또한 축전기를 형성할 수 있고 특별화된 회로는 인덕터처럼 보이는 op-amp를 가능하게 하여 전체의 모스펫으로 만들어서 다이오드를 제외하고 모든 일반 아날로그 소자를 가능하게 한다. (그리하여 모스펫보다 더 작게 만들 수 있다.) 이는 더좁은 공간으로 실리콘 칩 위에서 만들어지는 완벽한 아날로그 회로를 가능하게 한다. 어떤 집적회로는 하나의 칩 위에 아날로그와 디지털 모스펫 소자를 조합하여 필요한 기판 공간을 더 작게 만들었다. 이것은 칩 단계에서 아날로그 회로와 디지털 회로를 격리할 필요로 만들어서 격리링과 절연체 위의 실리콘 (Silicon-On-Insulator, SOI)이 사용되는 계기가 된다. 아날로그 설계 과정에서 접합형 트랜지스터 대 모스펫의 주요한 이점은 좁은 공간에서 대용량 전류를 처리하는 접합형 트랜지스터의 능력이다. 제조공정은 접합형 트랜지스터와 모스펫을 하나의 소자로 통합하는게 존재하며, 이런 혼합된 트랜지스터 소자가 하나의 BJT-FET를 포함하는 경우에는 양극성 전계효과 트랜지스터 (Bipolar-FET, Bi-FET)라고 부르며 상보성 BJT-FET를 포함하는 경우에는 양극성 시모스(Biplar-CMOS, BiCMOS)라고 부른다. 이 소자는 절연체 게이트와 고밀도 전류라는 이점을 모두 제공한다.

접합형 트랜지스터는 어떤 디지털 회로에서는 모스펫을 뛰어넘는 장점이 있다. 접합형 트랜지스터는 디지털 동작에서 적어도 두 가지 일을 더 잘한다. 첫 번째는 고속 스위칭이다. 왜냐하면 게이트에 "큰" 전기용량을 가지고 있지 않아서 채널의 저항과 곱하면 작은 고유 시간상수(T=RC)를 주기 때문이다. 고주파 신호를 차단하기 때문에 고유 시간상수는 모스펫이 동작하는 속도의 한계를 정한다. 채널을 넓히면 채널의 저항이 줄어들지만 정확히 동일한 양만큼 전기용량이 커진다. 채널 너비의 감소는 저항이 커지고 동일한 양만큼 전기용량이 작아진다. R*C=Tc1, 0.5R*2C=Tc1, 2R*0.5C=Tc1. 어떤 과정에서 고유 시간상수를 줄이는 방법은 없다. 채널 폭, 채널 높이, 게이트 두께, 재료를 다르게 하는 다른 과정은 고유 시간상수가 다르다. 접합형 트랜지스터는 게이트가 없기 때문에 이런 대부분의 문제가 없다. 두 번째 동작은 첫 번째로부터 유래된다. 여러 개의 다른 게이트를 작동시키는 것을 부채질(팬아웃, fanout)이라고 부르는데, 이때 모스펫의 저항은 다른 전계효과 트랜지스터의 게이트 전기용량과 직렬 연결되어 2차 시간상수를 준다. 지연 회로에서 훨씬 큰 다른 시모스 소자에 신호를 보내는 작은 시모스 소자를 사용하여 셋 신호 지연을 생성하는 데 이 사실을 이용한다. 인가하는 전계효과 트랜지스터의 채널 폭을 증가시켜 저항을 줄이고, 인가되는 전계효과 트랜지스터의 채널 폭을 줄여서 전기용량을 감소시킴으로써 2차 시간상수를 최소화할 수 있다. 이것은 인가하는 전계효과 트랜지스터의 전기용량을 증가시키고 인가되는 전계효과 트랜지스터의 저항을 증가시키는 단점이 있지만 일반적으로 이런 단점은 타이밍 문제와 비교했을 때 작은 문제이다. 접합형 트랜지스터는 다른 게이트를 인가하는 것이 좋다. 왜냐하면 모스펫보다 더 큰 전류를 출력할 수 있어서 전계효과 트랜지스터에 빠르게 전하를 인가하는 것이 가능하기 때문이다. 많은 칩은 모스펫 입력과 양극성 시모스 (한절위 참조)출력을 사용한다.

모스펫 축소

[편집]지난 수십 년간 모스펫의 크기가 지속적으로 감소되었다; 일반적으로 모스펫 채널 길이는 한 몇 마이크로미터였지만 현대의 집적 회로는 0.1 마이크로미터보다 더 작은 채널길이를 갖는 모스펫이 쓰인다. 실제로 인텔은 2006년에 65 nm 최소 배선폭 (심지어 채널은 더 짧음)을 지니는 공정의 생산을 시작했다. 1990년대 후반까지 이 크기 축소는 단점없이 모스펫 동작을 크게 개선하게 되었다. 역사적으로 모스펫 크기를 줄이는 데에 어려움은 반도체소자 제조 공정과 관련되었다.

모스펫 축소의 이유

[편집]소형 모스펫은 몇 가지 이유로 매력적이다. 첫째로 소형 모스펫은 넓이 치수가 짧아져서 더 많은 전류가 통하는 것을 가능하게 한다; 개념상으로 모스펫은 온상태에 있는 저항기와 같고 짧아진 저항기는 더 적은 저항값을 지닌다; 그렇지만 그들은 좁은 폭을 가지고 있어서 비율적으로 더 큰 저항값을 가지게 되는데 진짜 문제점은 단위면적당 저항을 줄이는 것이다. 두 번째로 소형 모스펫은 게이트 영역이 작고 따라서 게이트 전기용량이 작다. 축소된 모스펫은 얇은 게이트 유전체이여서 온상태 단위면적당 저항을 감소시키지만 단위면적당 게이트 전기용량은 커진다; 그럼에도 불구하고 이런 효과는 여전히 좋은 방향으로 간다. 첫 번째 두가지 요소는 짧은 스위칭 시간에 기여하여 빠른 처리 속도와 스위칭당 저전력 특징을 갖는다. 축소된 모스펫에서 세 번째 이유는 면적을 감소시켜서 비용을 감소시킨다. 소형 모스펫은 고밀도 패킹이 가능하여 소형칩이나 동일한 크기에서 계산능력이 뛰어난 칩이 된다. 반도체 웨이퍼에서 제조비용은 상대적으로 고정돼 있기 때문에 집적 회로당 비용은 웨이퍼당 생산할 수 있는 칩의 수와 주로 관련된다. 그러므로 소형 집적회로는 웨이퍼당 더많은 칩을 생산할 수 있어서 칩단가를 감소시킨다.

모스펫 축소 때문에 발생하는 어려움

[편집]마이크로미터보다 작은 채널길이를 갖는 모스펫의 생산은 도전이었고, 반도체 소자 제조에서의 문제점은 항상 집적회로 기술을 발전시키는 데 제한 요소이다. 최근에 모스펫이 작아져서 동작문제를 발생시켰다.

문턱아래 전도

[편집]모스펫이 작기 때문에, 신뢰도를 유지하기 위해 게이트에 인가될 수 있는 전압은 확실히 감소하여야 한다. 성능을 향상시키기 위해서 모스펫의 문턱전압도 또한 감소되어야 한다. 문턱전압이 감소되면 트랜지스터는 완벽하게 차단하지 못한다; 즉 트랜지스터는 미약한 역 형태(inversion mode)로 소스와 드레인사이에서 문턱아래 (누설)이나 문턱아래 전도처럼 동작한다. 과거에 무시되었던 문턱아래 전도가 이제는 고성능 VLSI 칩의 총 소비전력의 반이상을 차지할 수 있다.

어떤 저전력 아날로그 회로는 문턱아래 전도를 이용하도록 설계한다; 미약한 역 영역의 동작에 의하여 이런 회로에 있는 모스펫은 가능한 가장높은 트랜스컨덕턱스-전류 비율을 전송한다.

상호연결 전기용량

[편집]전통적으로 스위칭 시간은 게이트의 게이트 전기용량과 대충 비례한다. 그러나 트랜지스터가 점점 작아지고 더 많은 트랜지스터가 칩위에 배치되면서, 상호연결 전기용량 (칩의 다른 부분을 연결하는 전선의 커패시턴스)은 전기용랑에서 큰 비중을 차지하게 되었다. 신호는 상호연결을 통하여 전송되기 때문에 지연 증가와 성능 감소를 발생시킨다.

열 발생

[편집]집적회로위에 모스펫의 밀도가 계속 증가되어 회로동작을 손상시킬 수 있는 거대한 발열의 문제를 발생시킨다. 회로는 고온에서 느리게 동작하여 신뢰성을 떨어뜨리고 수명을 단축한다. 방열판과 다른 냉각 방법은 이제 마이크로프로세서를 포함하여 많은 집적회로에 필요하다.

전력 모스펫은 열폭주의 위험이 있다. 온상태 저항이 온도에 따라 증가함에 따라, 부하가 근사적으로 일정 전류를 소비하면 전력손실이 증가하고 따라서 더 많은 열을 발생시킨다. 방열판이 온도를 충분히 낮게 유지할 수 없으면 접합부 온도는 제어할 수 없을만큼 빠르게 상승하여 소자를 파괴시킨다.

게이트 산화물 누설

[편집]게이트와 채널사이에서 절연체 역할을 하는 게이트 산화막은 가능한 얇게 만들어야 하는데, 그것은 트랜지스터가 온일 때 채널 전도도와 성능을 향상시키고, 차단일때는 문턱아래 누설을 감소시키기 위해서이다. 그러나 1.2 nm 근처의 두께 (실리콘에서 ~5 원자 두께)를 가진 현재의 게이트 산화막에서는 게이트와 채널사이에 전자 투과라는 양자역학적 현상으로 인해 전력소비가 증가된다.

이산화 실리콘보다 더 큰 유전체 상수를 가진 절연체 (높은 k 유전체를 가리킴)가, 예를 들면 하프늄, 지르코늄 규산염 또는 산화물같은 그룹 IVb 금속 규산염이, 게이트 손실을 줄이기 위해 앞으로 사용될 것이다. 산화막 게이트 물질의 유전체 상수를 증가시키는 것은 높은 전기용량을 가졌지만 두꺼운 층을 가능하게 한다. 큰 두께는 게이트와 채널사이의 투과전류를 감소시킨다. 새로운 게이트 산화물의 장벽 높이를 중요하게 고려해야 한다; 반도체와 산화막사이의 전도띠 에너지 차이 (그리고 원자가띠에서 대응하는 에너지 차이)는 누설 전류 수준에도 영향을 미칠것이다. 전통적인 게이트 산화물 즉 이산화 실리콘의 장벽은 약 8 eV이다. 많은 대체 유전체의 장벽은 현저히 낮아서 높은 유전체 상수의 이점을 상쇄한다.

공정 변이

[편집]모스펫이 소형화되면서 다양한 트랜지스터 특징을 만들어내는 실리콘 원자의 수는 적어졌다. 칩을 제조하는 동안 일어나는 무작위의 공정 변이는 트랜지스터의 크기에 영향을 미칠 수 있는데, 트랜지스터가 소형화되면서 트랜지스터 전체 크기의 상당부분을 차지한다. 트랜지스터 특성이 덜 결정적으로 되고 더 통계적으로 된다. 이 통계적 변이는 설계의 어려움을 증가시킨다.

모스펫 구성

[편집]게이트 재료

[편집]게이트 금속의 첫 번째 기준은 좋은 전도이다. 고농도 도핑된 폴리실리콘은 수용가능하지만 확실히 이상적인 전도체는 아니고 이것 역시 표준 게이트 물질의 역할에서 약간의 기술적 결함으로 힘들다. 그럼에도 불구하고 게이트 재료로 폴리실리콘의 사용은 몇 가지 좋은 이유가 있다:

- 문턱전압 (과 동시에 드레인-소스 온전류)은 게이트 물질과 채널 물질사이의 일 함수 차이에 의하여 조정된다. 왜냐하면 폴리실리콘은 반도체이고 이것의 일 함수는 도핑의 형태와 수준을 조정해서 변형될 수 있기 때문이다. 더욱 폴리실리콘은 기본적인 실리콘 채널과 동일한 띠틈이고 일 함수를 조정하는 꽤 직접적인 방법이여서 엔모스와 피모스 소자에게 문턱전압을 낮게 한다. 상대적으로 금속의 일 함수는 쉽게 조정되지 않아서 낮은 문턱전압을 얻기 위해 일 함수를 조정하는 것은 중요한 도전이 된다. 추가로 피모스와 엔모스 소자에서 낮은 문턱소자를 얻는 것은 추가적인 복잡한 제조 공정을 포함하여 각 소자형태에 다른 금속의 사용을 요구할 것이다.

- 실리콘 SiO2 경계막은 연구되고 있고 관련된 몇 가지 결점을 지닌 것으로 알려진다. 상대적으로 많은 금속 절연체 경계막은 결점의 중요한 준위를 포함하여 페르미 준위 고정, 충전, 궁극적으로 소자성능을 떨어뜨리는 현상을 일으킨다.

- 모스펫 집적회로 제조 공정에서 고성능 트랜지스터를 만들기 위해서 확실한 고온단계 이전에 게이트 물질을 증착하는 편이 바람직하다. 어떤 금속은 고온단계에서 녹기 때문에 메탈-게이트 공정 기반에 사용하는 금속의 종류는 제한된다.

폴리실리콘 게이트가 지난 20년간 사실상 표준인 동안에 몇 가지 단점이 있어서 금속 게이트나 미래의 다른 물질로 대체할 수 있다. 이런 단점은 다음과 같다:

- 폴리실리콘은 좋은 전도체가 아니어서(대략 금속보다 1000배 더 큰 저항) 물질을 통과하는 신호의 전파속도를 감소시킨다. 저항값은 도핑의 단계를 증가시켜서 낮출 수 있지만 도핑된 폴리실리콘은 대부분의 금속처럼 전도되는 것은 아니다. 더 전도력을 향상시키기 위해 가끔씩 텅스텐, 티타늄, 코발트, 최근에는 니켈같은 고온금속은 폴리실리콘의 상위막으로 합금된다. 이렇게 혼합된 물질은 규화물이라고 부른다. 규화 폴리실리콘의 조합은 단독 폴리실리콘보다 전기적특성이 좋고 여전히 수반하는 공정에서 녹지 않는다. 또한 문턱전압은 단독 폴리실리콘보다 특별히 높지 않는다. 왜냐하면 규소 화합물은 채널 근처에 없기 때문이다. 공정에서 질화물 (실리사이드)는 게이트 전극과 소스를 형성하는 것이고 드레인 영역은 살리사이드(self-aligned silicide, salicide)라고 부른다.

- 트랜지스터가 극도하게 작아졌을 때 게이트 전극막을 최첨단 기술을 사용해서 1 nm 근처로 매우 작게 만들 필요가 있다. 여기서 관찰된 현상은 폴리 공핍이라고 부르며 공핍막은 게이트 유전층 옆에 게이트 폴리실리콘에서 트랜지스터가 반전되었을 때 형성된다. 이 문제를 해결하기 위해서 금속 게이트가 요구된다. 탄탈, 텅스텐, 질화 탄탈, 질화 텅스텐같은 다양한 금속 게이트는 일반적으로 높은 k 유전체와 결합됐다. 대안은 완전한 규화 폴리실리콘 게이트를 사용하는 것이고 공정은 FUSI를 뜻한다.

다른 모스펫 종류

[편집]이중 게이트 모스펫

[편집]이중 게이트 모스펫은 사극관 환경을 지녀서 소자에서 전류를 양쪽 게이트로 제어한다. 라디오 주파수 응용에서 소신호 소자에 일반적으로 사용돼서 두 번째 게이트는 일반적으로 증폭값 제어나 혼합과 주파수 변환에 사용된다.

공핍형 모스펫

[편집]"공핍형" 모스펫 소자가 있어서 이미 설명한 표준 "확장형" 소자보다 일반적으로 덜 사용된다. 이것들은 도핑된 모스펫 소자이여서 게이트에 어떤 전압을 인가하지 않아도 채널이 존재한다. 채널을 제어하기 위해서 음의 전압이 게이트에 걸리면 공핍된 채널은 감소되어 전류가 소자에 흐른다. 실제로 공핍형 소자는 일반적으로 닫힌 스위치와 동일하며 확장형 소자는 일반적으로 열린 스위치와 동일하다.[2] Archived 2007년 3월 11일 - 웨이백 머신

엔모스 논리

[편집]N채널 모스펫은 P채널 모스펫보다 작고 실리콘 기판에서 생산된 모스펫의 한가지 형태는 저렴하고 기술적으로 간단하다. 이것들은 N채널 모스펫을 한정적으로 사용한 엔모스 논리 설계의 강력한 원리이다. 그러나 시모스 논리와 다르게 엔모스 논리는 스위칭이 일어나지 않을때도 전력을 소비한다. 기술적으로 진보된 시모스 논리는 디지털 칩에 접합한 공정이 되기 위해 1980년대의 엔모스 논리를 대체했다.

전력 모스펫

[편집]

전력 MOSFET은 위에 보인 것보다 다른 구조를 가지고 있다.[10] 모든 전력소자의 구조는 수직이고 평판이 아니다. 수직구조를 사용한 이것은 차단되 고전압과 고전류를 유지하는게 가능한 트랜지스터이다. 트랜지스터의 전압등급은 도핑과 N에픽택시막 (단면 부분을 보세요) 두께의 기능이고 전류등급은 채널폭 (넓은 채널은 고전류)의 기능이다. 평판 구조에서 전류와 항복전압 등급은 "실리콘 재산"의 비효율적 사용으로인한 채널면적 (채널의 폭과 길이 각각)의 기능이다. 수직주조에서 소자면적은 유지할 수 있는 전류에 대충 비례하고 소자두께 (실제로는 N에픽택시막 두께)는 항복전압에 비례한다.

측면의 구조가 존재하는 전력 모스펫은 특별히 가치있다. 이것은 최상급 오디오 증폭기에 주로 사용된다. 장점은 포화영역 (접합형 트랜지스터의 선형영역과 일치됨)에서 수직형 모스펫보다 좋은 특성이다. 수직형 모스펫은 스위칭 응용에 설계되어서 통과와 차단상태에만 사용된다.

디모스

[편집]디모스는 이중으로 확산된 금속 산화막 반도체 (double-Diffused Metal Oxide Semiconductor)의 줄인말이다. 대부분의 전력 MOSFET은 이 기술을 이용하여 만든다.

모스펫 아날로그 스위치

[편집]모스펫 아날로그 스위치는 온일 때 아날로그 신호를 통과시키는 낮은저항 스위치같이 모스펫 채널을 사용하고 차단일 때 높은 임피던스같이 모스펫 채널을 사용한다. 신호는 모스펫 스위치를 교차하여 양쪽 방향으로 흐른다. 이 응용에서 모스펫의 드레인과 소스는 게이트와 비교한 각 전극의 전압에 따라서 위치를 서로 교환한다. 집적 다이오드가 존재하지 않는 간단한 모스펫에서 소스는 엔모스에서 좀 더 음의 측이고 피모스에서 좀 더 양의 측이다. 모든 이런 스위치는 게이트-소스, 게이트-드레인, 소스-드레인 전압에 의하여 어떤신호가 통과할지 차단할지가 제한되다; 초과된 제한전압은 잠재적으로 스위치를 손상시킬 것이다.

단독형 모스펫 스위치

[편집]아날로그 스위치는 N형이나 P형의 사단자의 단순한 모스펫을 사용한다. N형 스위치의 경우 보디는 가장 낮은 전원 (일반적으로 그라운드)에 연결되고 게이트는 스위치 제어로 사용된다. 게이트 전압이 문턱전압이상 소스전압을 초과할 때마다 모스펫은 전도된다. 더 높은 전압은 모스펫이 더욱 전도되게 한다. 엔모스는 (Vgate-Vtn)보다 낮은 모든전압은 통과할 것이다. 스위치가 전도되면 일반적으로 선형영역으로 동작된다. 왜냐하면 소스와 드레인 전압은 일반적으로 거의 비슷하기 때문이다.

피모스의 경우에 보디는 가장 높은 전압에에 연결되고 게이트는 낮은 전압이 스위치를 열게 한다. 피모스 스위치는 (Vgate+Vtp)보다 높은 모든전압은 통과한다.

피모스 스위치는 동일한 면적의 엔모스 소자 저항의 약 3배정도이다. 왜냐하면 전자는 실리콘에서 양공의 3배 이동도를 갖기 때문이다.

이중형 (시모스) 모스펫 스위치

[편집]스위치의 이 "상보성"이나 시모스형은 한가지형 스위치의 제한을 보완하기 위해 하나의 피모스와 하나의 엔모스 전계효과 트랜지스터를 사용한다. 전계효과 트랜지스터는 병렬로 연결된 드레인과 소스가 있으며 피모스의 보디는 고전압 (VDD)에 연결되어 있고 엔모스의 보디는 저전압 (GND)에 연결되어 있다. 피모스의 게이트에서 채널을 온하는 것은 저전압을 인가하는 것이고 엔모스의 게이트는 고전압을 인가하는 것이다. (VDD-Vtn)과 (Gnd+Vtp) 사이 전압의 모든 전계효과 트랜지스터는 신호를 전도하여 (Gnd+Vtp)보다 낮은 전압의 엔모스는 양공으로 전도되고 (VDD-Vtn)보다 높은 전압의 피모스는 양공으로 전도된다.

오직 이 스위치에서 제한은 모든 전계효과 트랜지스터에서 게이트-소스, 게이트-드레인, 소스-드레인 전압 제한이다. 또한 피모스는 일반적으로 엔모스의 3배 폭이여서 스위치는 안정될 것이다.

세가지 상태 논리는 낮은 저항에서 제공하는 출력, 높은 저항일 때 완전한 범위 출력, 차단일 때 중간급 신호에 가끔 시모스 모스펫 스위치로 통합된다.

참조

[편집]- ↑ 릴리언필드 (Lilienfeld), J. E., 미국특허 1,900,018 1928년 3월 28일 제기됨, 1933년 3월 7일 발표됨

- ↑ 엠시칼딘 (McCaldin)와 호어니 (Hoerni)는 독립적으로 평판 공정을 창안한다. 호어니는 1960년 워싱턴 디시 전자 소자 미팅에서 서류에 "평판 실리곤 트랜지스터와 다이오드"라고 표현했다.

- ↑ 킬비 (Kilby)와 노이스 (Noyce)는 독립적으로 창안한다. 노이스의 사망이후 2000년에 킬리는 노벨 물리학상을 받았다.

- ↑ 강, D.와 아탈라, M. M. (Atalla, M. M.은 IRE 고체 상태 소자 개발 및 발표, 피치버그, 1960년.

- ↑ 홉스테인 (Hofstein)과 헤이만 (Heiman), IEEE의 회보>, 1963년 9월.

- ↑ 윌리암 B. 쇼클리 (William B. Shockley), 존 바딘 (John Bardeen), 월터 H. 브래틴 (Walter H. Brattain), 1956년 노벨 물리학 수상

- ↑ 바우어 (Bower), 미국 특허 3,472,712, 1965년 7월 창안됨, 8월 27일 제기됨, 1966년 8월 14일 발표됨.

- ↑ R. W. 바우어 (R. W. Bower)와 H. G. 딜 (H. G. Dill), "소스-드레인 마스크처럼 게이트를 이용하여 제작된 저항층 게이트 전계효과 트랜지스터 (IGFET)", 페이지 16.6 국제 전자 소자 미팅, 워신턴 D.C., 1966년.

- ↑ F. 파킨 (F. Faggin)과 T. 클라인 (T. Klein), "실리콘 게이트 기술," 솔리드스테이트 일렉트로닉스, 제 13권, 1970년 8월, 페이지 1125-1144.

- ↑ 전력 반도체 소자, B. 자요트 발리거 (B. Jayant Baliga), PWS 출판사, 보스톤. ISBN 0-534-94098-6

외부 링크

[편집]- (영어) 모스펫 애플릿 - 모스펫을 이해하는 데 도움이 되는 매우 좋은 애플릿.

- (영어) 모스펫 모델 Archived 2020년 12월 1일 - 웨이백 머신 - 다이어그램과 수학적 유도.

- (영어) MIT 열린 코스웨어 6.002 Archived 2007년 2월 2일 - 웨이백 머신 - 회로학과 전자공학에 대한 MIT의 소개된 전자공학 과정을 연결.

- (영어) MIT 열린 코스웨어 6.012 - 모든 마이크로전자공학과 모스펫에 관한 MIT의 더상급 수업을 연결.