« Boîtier de circuit intégré » : différence entre les versions

Pld (discuter | contributions) m relecture |

|||

| (10 versions intermédiaires par 9 utilisateurs non affichées) | |||

| Ligne 1 : | Ligne 1 : | ||

[[Fichier:Ic-package-CDIP.svg|alt=Boîtier de circuit intégré de type CDIP à 24 broches.|vignette|Boîtier de circuit intégré de type CDIP à 24 broches.]] |

[[Fichier:Ic-package-CDIP.svg|alt=Boîtier de circuit intégré de type CDIP à 24 broches.|vignette|Boîtier de circuit intégré de type CDIP à 24 broches.]] |

||

Un '''boîtier de circuit intégré''' (ou ''package'') est un [[wikt:boîtier|boîtier]] servant à la fois de jonction électrique et d'interface mécanique entre la [[Die (circuit intégré)|puce]] du [[circuit intégré]] et le [[circuit imprimé]]. Il est généralement composé de [[Matière plastique|plastique]], parfois de [[céramique]], rarement de [[métal]]. Certains boîtiers possèdent des fenêtres transparentes permettant par exemple l'effacement par [[ultraviolet]] de certaines mémoires ([[Erasable Programmable Read Only Memory|EPROM]]). |

Un '''boîtier''' ou '''boitier<ref group="N">Selon les [[rectifications orthographiques du français en 1990]] [http://www.academie-francaise.fr/sites/academie-francaise.fr/files/rectifications_1990.pdf Rapport du conseil supérieur de la Langue française publié dans les documents administratifs du Journal officiel du 6 décembre 1990]</ref> de circuit intégré''' (ou ''package'') est un [[wikt:boîtier|boîtier]] servant à la fois de jonction électrique et d'interface mécanique entre la [[Die (circuit intégré)|puce]] du [[circuit intégré]] et le [[circuit imprimé]] (PCB). Il est généralement composé de [[Matière plastique|plastique]], parfois de [[céramique]], rarement de [[métal]]. Certains boîtiers possèdent des fenêtres transparentes permettant par exemple l'effacement par [[ultraviolet]] de certaines mémoires ([[Erasable Programmable Read Only Memory|EPROM]]). |

||

== Fonctions == |

== Fonctions == |

||

| Ligne 6 : | Ligne 6 : | ||

Le boîtier a différentes fonctions : |

Le boîtier a différentes fonctions : |

||

* Assurer la jonction électrique avec l'extérieur. Plusieurs solutions sont possibles : |

* Assurer la jonction électrique avec l'extérieur. Plusieurs solutions sont possibles : |

||

** Utilisation de ''pins'' qui vont être brasés au ''circuit imprimé'', par exemple les boîtiers [[Dual Inline Package|DIP]] ou [[Quad Flat Package|QFP]] |

** Utilisation de ''pins'' (broches) qui vont être brasés au ''circuit imprimé'', par exemple les boîtiers [[Dual Inline Package|DIP]] ou [[Quad Flat Package|QFP]] |

||

** Des plages dorées vont être brasées par apport de [[Crème à braser|pâte à braser]] lors du processus de brasage, par exemple les boîtiers [[QFN]] |

** Des plages dorées vont être brasées par apport de [[Crème à braser|pâte à braser]] lors du processus de brasage, par exemple les boîtiers [[QFN]] |

||

** Utilisation de billes de brasage pour faire la jonction entre le '''boîtier''' et le ''PCB'', ce sont les boîtiers [[Matrice de billes|BGA]]. |

** Utilisation de billes de brasage pour faire la jonction entre le '''boîtier''' et le ''PCB'', ce sont les boîtiers [[Matrice de billes|BGA]]. |

||

La jonction entre |

La jonction entre la puce et le boîtier peut se faire de deux manières : |

||

[[Image: |

[[Image:Intel 8742 153056995.jpg|right|250px|thumb|Exemple de bonding sur un circuit intégré [[Intel]] 8742]] |

||

# Soit par ''[[Câblage par fil|bonding]]'', c'est-à-dire l'utilisation de petits fils d'or ou d'aluminium de 15 à 50 µm pour réaliser la jonction entre les plages d'accueil du ''die'' aux ''pins''. L'ensemble est noyé dans une résine d'encapsulation. |

# Soit par ''[[Câblage par fil|bonding]]'', c'est-à-dire l'utilisation de petits fils d'or ou d'aluminium de 15 à 50 µm pour réaliser la jonction entre les plages d'accueil du ''die'' aux ''pins''. L'ensemble est noyé dans une résine d'encapsulation. |

||

# Soit par assemblage ''[[Puce retournée|flip-chip]]'' : Les plages d'accueil |

# Soit par assemblage ''[[Puce retournée|flip-chip]]'' : Les plages d'accueil de la puce sont recouvertes de billes d'or (quelques µm de diamètre), le tout est retourné et brasé sur le PCB |

||

* Assurer la dissipation thermique |

* Assurer la dissipation thermique |

||

{{Article détaillé|Résistance thermique}} |

{{Article détaillé|Résistance thermique}} |

||

| Ligne 19 : | Ligne 19 : | ||

== Classification == |

== Classification == |

||

Il existe plusieurs organismes de [[Normalisation (industrie et service)|normalisation]] de renom international pour catégoriser les boîtiers de composants électroniques : [[Joint Electron Device Engineering Council|JEDEC]], [[Japan Electronic Industry Development Association|EIAJ]] (''Electronic Industries Association of Japan''), [[Mil standards]] (Standards militaires US), |

Il existe plusieurs organismes de [[Normalisation (industrie et service)|normalisation]] de renom international pour catégoriser les boîtiers de composants électroniques : [[Joint Electron Device Engineering Council|JEDEC]], [[Japan Electronic Industry Development Association|EIAJ]] (''Electronic Industries Association of Japan''), [[Mil standards]] (Standards militaires US), {{lien|lang=en|trad=SEMI|SEMI}} (''Semiconductor Equipment and Materials Institute''), [[American National Standards Institute|ANSI]]/[[IPC]] (''Interconnecting and Packaging Electronic Circuits Standards''). |

||

Le JEDEC spécifie des familles standard : [[Matrice de billes|BGA]], [[Matrice de colonnes|CGA]], DIM, [[Dual Inline Package|DIP]], DSO, DSB, [[Matrice de pastilles|LGA]], [[Matrice de broches|PGA]], QFF, QFJ, [[Quad Flat No-leads package|QFN]], [[Quad Flat Package|QFP]], SIM, [[Single Inline Package|SIP]], SOF, SOJ, SON, SVP, UCI, WLB, ZIP<Ref name="JEDEC">{{en}} [http://www.jedec.org/download/search/jesd30D.pdf JEDEC - Standard 30D - Descriptive Designation System for Semiconductor-device Packages (july 2006)]{{pdf}}</Ref>. |

Le JEDEC spécifie des familles standard : [[Matrice de billes|BGA]], [[Matrice de colonnes|CGA]], DIM, [[Dual Inline Package|DIP]], DSO, DSB, [[Matrice de pastilles|LGA]], [[Matrice de broches|PGA]], QFF, QFJ, [[Quad Flat No-leads package|QFN]], [[Quad Flat Package|QFP]], SIM, [[Single Inline Package|SIP]], SOF, SOJ, SON, SVP, UCI, WLB, ZIP<Ref name="JEDEC">{{en}} [http://www.jedec.org/download/search/jesd30D.pdf JEDEC - Standard 30D - Descriptive Designation System for Semiconductor-device Packages (july 2006)]{{pdf}}</Ref>. |

||

| Ligne 45 : | Ligne 45 : | ||

=== Matériaux === |

=== Matériaux === |

||

Dans la classification JEDEC<Ref name="JEDEC"/>, on peut trouver des boîtiers céramique (''C'' lorsque scellés par du métal, ''G'' lorsque scellés par du verre), des boîtiers métal (''M''), en plastique moulé (''P''), en silicone (''S''), ou en ruban [[polyimide]]<!--Oui, bien polyimide--> (''T''). Cette lettre est généralement en préfixe. |

Dans la classification JEDEC<Ref name="JEDEC"/>, on peut trouver des boîtiers céramique (''C'' lorsque scellés par du métal, ''G'' lorsque scellés par du verre), des boîtiers métal (''M''), en plastique moulé (''P''), en [[silicone]] (''S''), ou en ruban [[polyimide]]<!--Oui, bien polyimide--> (''T''). Cette lettre est généralement en préfixe. |

||

=== Broches === |

=== Broches === |

||

La forme des broches est codifiée par la norme JEDEC sous forme d'une lettre généralement en suffixe : On trouve les billes (''B''), les pattes recourbées (''C'', par exemple le boitier [[Plastic Leaded Chip Carrier|PLCC]], Gull-wing ''G'', tels que sur les boîtiers [[SOIC]]), J-Bend, L-Bend, S-Bend, J-inversé |

La forme des broches est codifiée par la norme JEDEC sous forme d'une lettre généralement en suffixe : On trouve les billes (''B''), les pattes recourbées (''C'', par exemple le boitier [[Plastic Leaded Chip Carrier|PLCC]]), Gull-wing (''G'', tels que sur les boîtiers [[Small-outline integrated circuit|SOIC]]), J-Bend, L-Bend, S-Bend, J-inversé, les oreilles pour la soudure de fils (''D'', ''H''), à plat (''F''), isolés (''I''), sans pattes (''N'', avec des plages de soudure tels les [[QFN]]), pattes traversantes (''P'', ''T''), à insertion rapide (''Q'', par exemple pour des [[Relais électromécanique|relais électromécaniques]]), à [[Wrapper (électronique)|wrapper]] (''W''), sortie filaire (''W''), ou à visser (''Y''). |

||

<gallery mode="packed"> |

<gallery mode="packed"> |

||

Fichier:XC68020 bottom p1160085.jpg|Pins ''P'' |

Fichier:XC68020 bottom p1160085.jpg|Pins ''P'' |

||

| Ligne 77 : | Ligne 77 : | ||

== Brochage == |

== Brochage == |

||

En [[électronique]] tout comme en [[électrotechnique]], le '''[[Brochage ( |

En [[électronique (technique)|électronique]] tout comme en [[électrotechnique]], le '''[[Brochage (électronique)|brochage]]''' d'un composant décrit le rôle de chacune des [[#Brochage|broche]]s d'un [[Connectique|connecteur]] ou d'un composant du plus simple au plus complexe des [[Circuit intégré|circuits intégrés]]. Le terme de brochage est synonyme de ''diagramme de connexion''. |

||

Le brochage est plus ou moins complexe : |

Le brochage est plus ou moins complexe : |

||

| Ligne 83 : | Ligne 83 : | ||

[[Image:TO-220 Front Coloured.svg|150px|right]] |

[[Image:TO-220 Front Coloured.svg|150px|right]] |

||

* Le brochage le plus simple est celui d'une [[diode]] (deux broches : [[anode]] et [[cathode]]) ensuite viennent les [[transistor]]s (trois broches), |

* Le brochage le plus simple est celui d'une [[diode]] (deux broches : [[anode]] et [[cathode]]) ensuite viennent les [[transistor]]s (trois broches), |

||

* Les brochages les plus complexes sont ceux des [[microprocesseur]]s. |

* Les brochages les plus complexes sont ceux des [[microprocesseur]]s. |

||

Les différents types de boîtiers de circuits intégrés induisent des brochages très différents. |

Les différents types de boîtiers de circuits intégrés induisent des brochages très différents. |

||

| Ligne 92 : | Ligne 92 : | ||

La plupart des [[Circuit intégré|circuits intégrés]] possèdent au moins deux broches reliées au « bus d'alimentation » du circuit sur lequel ils sont installés. |

La plupart des [[Circuit intégré|circuits intégrés]] possèdent au moins deux broches reliées au « bus d'alimentation » du circuit sur lequel ils sont installés. |

||

La broche d'alimentation positive repérée <math>V_\mathrm{CC+}</math> est parfois aussi appelée <math>V_\mathrm{DD}</math>, <math>V_\mathrm{CC}</math>, ou ''V''<sub>S+</sub>. La broche d'alimentation négative repérée <math>V_\mathrm{CC-} </math> est parfois aussi appelée <math>V_\mathrm{SS}</math>, <math>V_\mathrm{EE} </math>, ou ''V''<sub>S−</sub>. |

La broche d'alimentation positive repérée <math>V_\mathrm{CC+}</math> est parfois aussi appelée <math>V_\mathrm{DD}</math>, <math>V_\mathrm{CC}</math>, ou ''V''<sub>S+</sub>. La broche d'alimentation négative repérée <math>V_\mathrm{CC-} </math> est parfois aussi appelée <math>V_\mathrm{SS}</math>, <math>V_\mathrm{EE} </math>, ou ''V''<sub>S−</sub>. |

||

Le caractère doublé qui se trouve en indice de la lettre ''V'' fait référence au nom de la broche du transistor à laquelle cette alimentation sera généralement reliée<ref>{{en}} [http://www.maxim-ic.com/glossary/index.cfm/Ac/V/ID/943/Tm/VEE/ln/en Maxim-IC - Electrical Engineering Glossary Definition for Vcc]</ref>. |

Le caractère doublé qui se trouve en indice de la lettre ''V'' fait référence au nom de la broche du transistor à laquelle cette alimentation sera généralement reliée<ref>{{en}} [http://www.maxim-ic.com/glossary/index.cfm/Ac/V/ID/943/Tm/VEE/ln/en Maxim-IC - Electrical Engineering Glossary Definition for Vcc]</ref>. |

||

Ainsi, les appellations <math>V_\mathrm{CC} </math> et <math>V_\mathrm{EE} </math> sont généralement réservées aux AOP [[Transistor bipolaire|bipolaire]] tandis que les appellations <math>V_\mathrm{DD}</math> et <math>V_\mathrm{SS}</math> sont généralement réservées aux AOP à [[Transistor à effet de champ|effet de champ]]. |

Ainsi, les appellations <math>V_\mathrm{CC} </math> et <math>V_\mathrm{EE} </math> sont généralement réservées aux AOP [[Transistor bipolaire|bipolaire]] tandis que les appellations <math>V_\mathrm{DD}</math> et <math>V_\mathrm{SS}</math> sont généralement réservées aux AOP à [[Transistor à effet de champ|effet de champ]]. |

||

Le C de <math>V_\mathrm{CC}</math> signifie que l'alimentation est reliée au [[Collecteur et émetteur |

Le C de <math>V_\mathrm{CC}</math> signifie que l'alimentation est reliée au [[Collecteur et émetteur|collecteur]] d'un transistor bipolaire tandis que le E de <math>V_\mathrm{EE}</math> signifie que l'alimentation est reliée à l'[[Collecteur et émetteur|émetteur]] d'un transistor bipolaire. Le D de <math>V_\mathrm{DD}</math> fait référence au [[Drain et source|drain]] d'un transistor à effet de champ tandis que le S de <math>V_\mathrm{SS}</math> fait référence à la [[Drain et source|source]] de ce même transistor. |

||

== Caractérisation == |

== Caractérisation == |

||

| Ligne 138 : | Ligne 138 : | ||

== Notes et références == |

== Notes et références == |

||

=== Note === |

|||

{{Références|groupe="N"}} |

|||

=== Références === |

|||

{{Références}} |

{{Références}} |

||

| Ligne 157 : | Ligne 161 : | ||

{{Traduction/Référence|en|IC power supply pin|107282889}} |

{{Traduction/Référence|en|IC power supply pin|107282889}} |

||

{{Portail|électricité et électronique| |

{{Portail|électricité et électronique|micro et nanotechnologie}} |

||

{{DEFAULTSORT:Boitier de circuit integre}} |

{{DEFAULTSORT:Boitier de circuit integre}} |

||

Dernière version du 28 avril 2024 à 16:27

Un boîtier ou boitier[N 1] de circuit intégré (ou package) est un boîtier servant à la fois de jonction électrique et d'interface mécanique entre la puce du circuit intégré et le circuit imprimé (PCB). Il est généralement composé de plastique, parfois de céramique, rarement de métal. Certains boîtiers possèdent des fenêtres transparentes permettant par exemple l'effacement par ultraviolet de certaines mémoires (EPROM).

Fonctions

[modifier | modifier le code]Le boîtier a différentes fonctions :

- Assurer la jonction électrique avec l'extérieur. Plusieurs solutions sont possibles :

- Utilisation de pins (broches) qui vont être brasés au circuit imprimé, par exemple les boîtiers DIP ou QFP

- Des plages dorées vont être brasées par apport de pâte à braser lors du processus de brasage, par exemple les boîtiers QFN

- Utilisation de billes de brasage pour faire la jonction entre le boîtier et le PCB, ce sont les boîtiers BGA.

La jonction entre la puce et le boîtier peut se faire de deux manières :

- Soit par bonding, c'est-à-dire l'utilisation de petits fils d'or ou d'aluminium de 15 à 50 µm pour réaliser la jonction entre les plages d'accueil du die aux pins. L'ensemble est noyé dans une résine d'encapsulation.

- Soit par assemblage flip-chip : Les plages d'accueil de la puce sont recouvertes de billes d'or (quelques µm de diamètre), le tout est retourné et brasé sur le PCB

- Assurer la dissipation thermique

- Protéger la puce de l'environnement hostile (chocs, poussière, rayonnements)

- Adapter le composant aux contraintes de fabrication : on passe généralement d'un pas entre pins de l'ordre de la centaine de µm[1] au mm. Les contraintes de brasage sont également optimisées (température de brasure plus élevée, procédés standard de brasage par refusion/brasage à la vague).

Classification

[modifier | modifier le code]Il existe plusieurs organismes de normalisation de renom international pour catégoriser les boîtiers de composants électroniques : JEDEC, EIAJ (Electronic Industries Association of Japan), Mil standards (Standards militaires US), SEMI (en) (Semiconductor Equipment and Materials Institute), ANSI/IPC (Interconnecting and Packaging Electronic Circuits Standards).

Le JEDEC spécifie des familles standard : BGA, CGA, DIM, DIP, DSO, DSB, LGA, PGA, QFF, QFJ, QFN, QFP, SIM, SIP, SOF, SOJ, SON, SVP, UCI, WLB, ZIP[2].

Les boîtiers spécifiques sont définis suivant plusieurs paramètres.

TS – P DSO 2 – 44(50) / 5.3x10.2-1.27 -- - --- - ------ ------------- | | | | | | | | | | | Informations supplémentaires | | | | Nombre de broches | | | Différenciation supplémentaire pour les boîtiers SOJ/SON/DSO | | Famille (3 lettres obligatoires) | Matériau Fonctions spécifiques (0-6 lettres)

Style de contour

[modifier | modifier le code]Il s'agit du code basique définissant la famille de boîtier : cylindrique (CY), bouton (DB), grid array (GA), IM In-Line Module(IM), IP In-Line Package(IP), Press-Pack / Press-Fit (CP/PF, boîtier assemblé à la presse sans soudure), quad flatpack (QF, broches sur les 4 côtés du boîtier), small outline (SO, broches sur 2 côtés opposés du boîtier), CMS vertical (VP), boîtier sur Die/Wafer (DS/WL), montage sur collerette (FM), forme allongée (LF), assemblage microélectronique (MA), montage à clous (PM), boitier spécifique (SS), boîtier non classifié (UC).

Fonctions spécifiques

[modifier | modifier le code]Certaines fonctionnalités non communes sont définies par la classification JEDEC sous la forme d'un préfixe de 0 à 6 lettres suivi d'un tiret[2], on trouve notamment les fenêtres optiques (C), les die empilés dans un même boîtier (A, stacked package assembly), les dissipateurs de chaleur (H), ainsi que des codes pour la hauteur du boîtier ou le pas entre broches lorsqu'ils ne sont pas conformes au standard.

Matériaux

[modifier | modifier le code]Dans la classification JEDEC[2], on peut trouver des boîtiers céramique (C lorsque scellés par du métal, G lorsque scellés par du verre), des boîtiers métal (M), en plastique moulé (P), en silicone (S), ou en ruban polyimide (T). Cette lettre est généralement en préfixe.

Broches

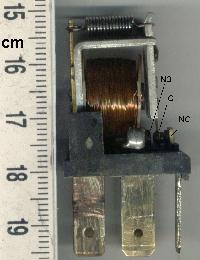

[modifier | modifier le code]La forme des broches est codifiée par la norme JEDEC sous forme d'une lettre généralement en suffixe : On trouve les billes (B), les pattes recourbées (C, par exemple le boitier PLCC), Gull-wing (G, tels que sur les boîtiers SOIC), J-Bend, L-Bend, S-Bend, J-inversé, les oreilles pour la soudure de fils (D, H), à plat (F), isolés (I), sans pattes (N, avec des plages de soudure tels les QFN), pattes traversantes (P, T), à insertion rapide (Q, par exemple pour des relais électromécaniques), à wrapper (W), sortie filaire (W), ou à visser (Y).

-

Pins P

-

Billes B

-

Pattes recourbées C

-

Sans pattes N

-

Gull-wing G

-

J-Bend J

-

Pins « through hole » T

-

Wrapping W

-

À oreilles D

-

À insertion rapide Q

-

À visser Y

Position des broches

[modifier | modifier le code]La norme JEDEC définit un préfixe représentant la position des broches par rapport à un circuit :

- rectangulaire ou carré : single (S, un seul côté), dual (D, sur 2 côtés opposés), quad (Q, sur les 4 côtés du boîtier), zig-zag (Z, en quinconce sur un côté), bottom (B), colonne (C), perpendiculaire (P)

- cylindrique : axiale (A), radiale (R), endcaps (E, extrémités de boîtiers cylindriques)

-

Single S

-

Dual D

-

Quad Q

-

Zig-zag Z

Brochage

[modifier | modifier le code]En électronique tout comme en électrotechnique, le brochage d'un composant décrit le rôle de chacune des broches d'un connecteur ou d'un composant du plus simple au plus complexe des circuits intégrés. Le terme de brochage est synonyme de diagramme de connexion.

Le brochage est plus ou moins complexe :

- Le brochage le plus simple est celui d'une diode (deux broches : anode et cathode) ensuite viennent les transistors (trois broches),

- Les brochages les plus complexes sont ceux des microprocesseurs.

Les différents types de boîtiers de circuits intégrés induisent des brochages très différents.

Broches d'alimentation d'un circuit intégré

[modifier | modifier le code]

La plupart des circuits intégrés possèdent au moins deux broches reliées au « bus d'alimentation » du circuit sur lequel ils sont installés.

La broche d'alimentation positive repérée est parfois aussi appelée , , ou VS+. La broche d'alimentation négative repérée est parfois aussi appelée , , ou VS−.

Le caractère doublé qui se trouve en indice de la lettre V fait référence au nom de la broche du transistor à laquelle cette alimentation sera généralement reliée[3]. Ainsi, les appellations et sont généralement réservées aux AOP bipolaire tandis que les appellations et sont généralement réservées aux AOP à effet de champ.

Le C de signifie que l'alimentation est reliée au collecteur d'un transistor bipolaire tandis que le E de signifie que l'alimentation est reliée à l'émetteur d'un transistor bipolaire. Le D de fait référence au drain d'un transistor à effet de champ tandis que le S de fait référence à la source de ce même transistor.

Caractérisation

[modifier | modifier le code]Caractérisation électrique

[modifier | modifier le code]La technique du pontage entraîne l'apparition de circuits RLC dont les caractéristiques ne sont pas négligeables pour des composants travaillant en haute fréquence. Les modèles de simulation IBIS ou SPICE prennent en compte ce paramètre.

Voici un ordre d'idées des caractéristiques d'un pontage standard[4], utilisant des fils d'or de 25,4 µm de diamètre :

| Caractéristique | Valeur pour L=2 mm |

Valeur pour L=5 mm |

|---|---|---|

| Résistance | 0,103 Ω | 0,257 Ω |

| Inductance | 1,996 nH | 5,869 nH |

| Capacité | 0,122 pF | 0,242 pF |

| Inductance mutuelle | 0,979 nH | 3,318 nH |

| Capacité mutuelle | 26,1 fF | 48,8 fF |

Caractérisation thermique

[modifier | modifier le code]Cette caractérisation est très importante en électrotechnique, mais aussi en électronique numérique. Le facteur de dissipation du boîtier peut déterminer certaines caractéristiques qui sont liées à la température comme la vitesse d'exécution d'un processeur, ou le courant de commutation d'un transistor.

Caractérisation électromagnétique

[modifier | modifier le code]Les boîtiers peuvent être conçus pour limiter le rayonnement électronique du composant qu'ils enveloppent (agresseur), ou au contraire limiter l'effet de l'environnement extérieur sur leur fonctionnement (victime). Certains secteurs d'activité tels que l'aéronautique, le spatial ou le secteur automobile font des études très poussées sur la caractérisation électromagnétique des boîtiers électroniques[5].

Notes et références

[modifier | modifier le code]Note

[modifier | modifier le code]Références

[modifier | modifier le code]- (en) ASEMEP 1999 Proceedings - 70-Micron Pad Pitch Capability/Fan-out (Determining Other Critical Parameters) « Copie archivée » (version du sur Internet Archive)

- (en) JEDEC - Standard 30D - Descriptive Designation System for Semiconductor-device Packages (july 2006)[PDF]

- (en) Maxim-IC - Electrical Engineering Glossary Definition for Vcc

- Données techniques de la société MOSIS

- (en) LESIA - cours sur la Compatibilité électromagnétique des circuits intégrés

Voir aussi

[modifier | modifier le code]Articles connexes

[modifier | modifier le code]- Composant électronique

- Composant monté en surface

- microprocesseur

- microcontrôleur

- Liste des principaux fabricants de semi-conducteurs au fil des ans

Liens externes

[modifier | modifier le code]- Technologies de bonding (pontage)

- Caractérisation électrique des boîtiers par Samsung [PDF]

- Caractérisation thermique des boîtiers par Samsung [PDF]

- Étude de l'encapsulation chez Intel

- Méthode de modélisation des boîtiers chez AMD (Samsung)

- (en) Cet article est partiellement ou en totalité issu de l’article de Wikipédia en anglais intitulé « IC power supply pin » (voir la liste des auteurs).